Assembly and Integration of IP for Front-end SoC Design

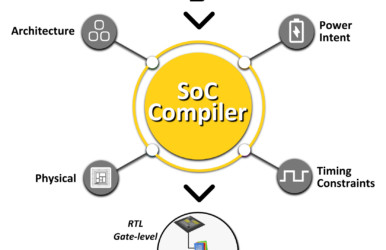

Defacto Technologies today announces v9 of their EDA software offering, SoC Compiler, replacing the STAR product name. Front-end SoC designers are faced with the daunting task of meeting electronic system requirements by choosing an appropriate architecture, re-using IP blocks, setting a power budget, meeting chip timing constraints and taking into account the physical design process.

The semiconductor industry has responded to these challenges by adopting several standards used in the SoC design process, like:

- Design data, RTL or Gate level

- IP block descriptions, IP-XACT

- Power Intent, UPF

- Physical, LEF/DEF

- Timing constraints, SDC

Many SoC design groups have been supported by internal CAD engineers that manage to piece together scripts and sub-flows for front-end design that aim to automate SoC creation and assembly, generate RTL and design collaterals, and get their designs ready for logic synthesis. This method of internal EDA tool development is often inefficient and not unified.

“With the SoC Compiler, v9 tools we have automated the process of building IP, SoC creation and integration for the front-end, getting RTL and design collaterals ready for logic synthesis much quicker, with more confidence and flexibility than ad-hoc approaches,” said Chouki Aktouf, CEO of Defacto Technologies. “Our design platform has reached a maturity level and includes capabilities to answer most of the challenges of front-end design teams. We renamed our product as SoC Compiler to better communicate what our tools are doing.”

With the increasing complexity of SoCs and the growing market demands in terms of lower costs and shorter turn-around times, Defacto’s SoC Compiler helps engineers face these challenges.

Anand Bariya, SVP Engineering at OpenFive said, “The Defacto SoC Compiler is helping our engineers at two levels. The first is during the SoC integration process to analyze the design, extract design information, and then effectively guide users to take the right decision when inserting connectivity in RTL. During the connectivity reporting and insertion process, we particularly appreciate the flexibility of APIs and the customization level when building Tcl or Python scripts. Next, the design for the back-end is where we are benefiting, detection and insertion of feedthrough connectivity are now fully automated. We are looking forward to extending the joint collaboration to other areas around SoC design.”

“As SoC design complexity keeps increasing the importance of a fully automated IP insertion including connectivity becomes critical,” said Philippe Notton, CEO at Sipearl. “We were recommended by a key industry stakeholder to use SoC Compiler for the SoC Integration process including their IP, so we evaluated it and adoption was smooth thanks to the maturity of the technology and the outstanding level of support. We successfully built a fully automated design assembly flow including IP insertion, IP stitching, design modification and top-level views generation.”

The Defacto SoC Compiler fits into existing EDA tools flows from all major vendors by adhering to industry standard file formats and providing APIs to customize the automation for evolving design methodologies.

Availability

More details about SoC Compiler v9 are available online (https://www.defactotech.com/products-solutions)

About Defacto Technologies

Founded in 2003, this Grenoble-based EDA software company has focused on offering tools for front-end designers that need to do design restructuring, IP integration and SoC building. They are active members in the Accellera Systems Initiative, and support industry standards: IP-XACT, LEF/DEF, UPF, SDC. Learn more at www.defactotech.com . Sales distributors are in the USA, Japan, Taiwan, South Korea, India and Israel.